УДК 621.3.049.75

## Г.В. Мылов, И.В. Дрожжин

## СНИЖЕНИЕ ПЛОТНОСТИ МЕЖСОЕДИНЕНИЙ МНОГОСЛОЙНЫХ ПЕЧАТНЫХ ПЛАТ

Предлагаются способ снижения плотности межсоединений многослойных печатных плат с высокой степенью интеграции топологического рисунка на этапе автоматизированного конструкторско-технологического проектирования путем перемещения переходных отверстий под микросхемой непосредственно под выводы микросхемы и технология изготовления многослойной печатной платы согласно приведенному способу. Результаты данной работы позволят разместить электрическую схему на печатной плате с меньшими габаритными размерами, использовать микросхемы BGA с меньшим шагом, снизить слойность печатной платы, повысить надежность межсоединений, избежать замыканий при установке планарных микросхем и микросхем BGA.

**Ключевые слова:** печатная плата, плотность межсоединений, микросхема, переходное отверстие, контактная площадка, послойное наращивание, заращивание отверстий.

Введение. При изготовлении уникальной аппаратуры с высокой надежностью происходит постоянное столкновение интересов разработчика и производителя. С одной стороны, стоит задача увеличения степени интеграции изделия и повышения плотности электрических межсоединений, с другой - необходимость сохранить технологичность изготавливаемой продукции. Поэтому важнейшей задачей производителей многослойных печатных плат является снижение плотности межсоединений при их изготовлении, что дает возможность сохранить технологичность, разместить электрическую схему на печатной плате с меньшими габаритными размерами, использовать микросхемы BGA с меньшим шагом, снизить слойность печатной платы, повысить надежность межсоединений, избежать замыканий при установке планарных микросхем и микросхем BGA с использованием поверхностного монтажа. Кроме того, для большой номенклатуры выпускаемой продукции, безусловно, необходимо наличие продуктов автоматизации на основе вновь разрабатываемых современных алгоритмов и математического аппарата, удовлетворяющих требованиям передовых технологий производства изделий электроники.

Развитие микроэлектронных компонентов характеризуется увеличением плотности активных элементов на кристалле примерно на 75% в год, а это, в свою очередь, вызывает необходимость в увеличении количества их выводов на

корпусе на 40% в год. Это обусловливают постоянно растущий спрос на новые методы корпусирования, позволяющие увеличить плотность межсоединений на печатной плате. Поэтому все большую популярность получают компоненты в матричных типах корпусов. Это корпуса типа LGA (Land Grid Array), BGA (Ball Grid Array), CGA (Column Grid Array). BGA корпуса позволяют оптимальным образом разместить большое количество выводов на ограниченной площади, обеспечивая все необходимые технологические нормы при монтаже.

Небольшие размеры, особенно в случае применения микросхем с малым шагом, снижают затраты на их производство. Расположение всех выводов в одной плоскости, с нижней стороны корпуса BGA, позволяет получить длину цепей более короткую, чем у микросхем, имеющих другие конструктивные исполнения. Это приводит к снижению паразитных излучений и, как следствие, положительно сказывается на целостности сигналов.

В результате общих тенденций, площадь монтажных подложек уменьшается примерно на 7 %, а физические размеры электронной аппаратуры на 10–20 % в год. Эта тенденция поддерживается непрерывным увеличением плотности межсоединений за счет уменьшения элементов печатного монтажа, пространственного распределения межслойных переходов за счет использования сквозных, глухих, слепых отвер-

стий. Все это серьезно влияет на облик производства печатных плат — увеличиваются стоимость основных фондов, объем прямых издержек, цикл производства. В конечном итоге все это приводит к увеличению себестоимости плат.

**Целью работы** является разработка способа снижения плотности межсоединений многослойной печатной платы без увеличения габаритного размера изделия для дополнительного увеличения степени интеграции топологии проводящего рисунка.

**Теоретические исследования.** Из уровня техники известны несколько типов конструкций многослойных печатных плат [1, 2]. Однако все они имеют следующие наиболее выраженные недостатки:

- высокая трудоемкость изготовления при низкой надежности изделия при производстве печатных плат с высокой степенью интеграции из-за снижения зазоров между элементами топологии проводящего рисунка;

- увеличение интеграции платы без снижения плотности межсоедиений, т.е. для печатных плат с высокой плотностью размещения топологии электропроводящего рисунка данное решение потребует значительного увеличения габаритов устройства.

Кроме того, при существующем методе размещения микросхемы BGA понятие "шаг микросхемы" можно считать условным. Фактически можно провести печатные дорожки по верхнему слою только с двух-трех наружных рядов выводов, а для остальных сигналов необходимо устанавливать переходные отверстия возле контактных площадок, что не позволяет в полной мере использовать все преимущества компонентов в матричных типах корпусов.

Существует четыре пути повышения степени интеграции топологического рисунка и монтажа компонентов на печатных платах для решения вопросов увеличения производительности выпускаемых изделий:

- уменьшение размера отверстий и контактных площадок, чтобы высвободить пространство для трассировки проводников;

- увеличение количества трасс между отверстиями за счет уменьшения ширины проводников и зазоров;

- увеличение количества слоев;

- введение многоуровневых межсоединений: отказ от сквозных отверстий в пользу глухих и слепых межслойных переходов.

Основное препятствие на пути увеличения плотности межсоединений — это контактные площадки большого диаметра, они уменьшают трассировочное пространство между отверстия-

ми. Размер контактных площадок определяется операцией сверления отверстий. Чем больше погрешность пространственного совмещения элементов межсоединений, тем больше должен быть размер контактных площадок, чтобы обеспечить уверенное попадание в них сверла. Поэтому контактные площадки вокруг просверленных отверстий компенсируют любые возможные смещения элементов межсоединений в слоях относительно друг друга и не допускают сверления отверстия за пределами контактной площадки. Погрешность совмещения в основном вызывается размерной нестабильностью базового материала и смещением основания на различных этапах производства печатных плат.

Для того чтобы контактная площадка выполняла предназначенные ей функции, она должна охватывать металлизированное переходное отверстие. Если сквозное отверстие выходит за пределы контактной площадки, возникает вероятность стыкового соединения торца проводника с металлизацией отверстия. Такое соединение непрочно и может быть оборвано или при пайке, или позже - при воздействии эксплуатационных факторов (термоциклы, вибрация и т.п.). Поэтому считается, что надежное соединение обеспечивается лишь при наличии гарантийного пояска отверстия контактной площадкой. Его минимальный размер обычно принимается равным толщине фольги и рассчитывается из условия обеспечения минимальной ширины гарантийного пояска с учетом всех неизбежных погрешностей производства.

Некоторый выигрыш в уменьшении размера контактной площадки и в соответствующем увеличении трассировочного пространства можно получить за счет удлинения ее формы в сторону подхода проводника к контактной площадке. В этом случае практически не изменяется трассировочная способность, но существенно расширяется допуск на смещение переходного отверстия. Двукратное уменьшение диаметра контактной площадки дает трехкратный выигрыш в плотности разводки, что на практике позволяет избавиться как минимум от половины сигнальных слоев и вследствие этого от половины слоев земли и питания ПП [3].

Очевидно, что уменьшение ширины проводников и зазоров позволяет увеличить количество трасс на каждом слое платы. Но все же уменьшать ширину проводников бесконечно невозможно. Такое уменьшение ограничено токонесущими свойствами и омическим сопротивлением проводников. Омическое сопротивление еще в большей степени сказывается на работоспособности схем, когда они имеют большую длину

трасс, что для печатных плат не редкость. Существуют и технологические ограничения на ширину проводников, связанные непосредственно с производственным процессом. Выход готовой продукции резко падает, если требования к производственным процессам не укладываются в рамки нормальных допусков, определяемых применяемым оборудованием, материалами и параметрами климатической зоны производственных помещений.

Имеются ограничения и на уменьшение расстояний между проводниками (изоляционные зазоры). Тем не менее, если удалось достичь уменьшения ширины проводников с учетом описанных ограничений, то это позволит эффективно влиять на плотность межсоединений и снижение себестоимости производства печатных плат. При уменьшении ширины проводников существенно уменьшается число слоев, необходимое для сигнальной разводки, при условии, что выход годной продукции, плотность межсоединений и площадь платы остаются постоянными. Уменьшение числа слоев может существенно снизить затраты на производство печатных плат.

Когда не хватает места на существующих слоях для размещения всех необходимых межсоединений, добавляют еще один слой. Это самое простое решение. Такой подход широко применялся в прошлом. Но сейчас, когда эффективность затрат на изготовление подложек имеет большое значение, необходим тщательный анализ каждого проекта минимизации числа слоев, так как с каждым дополнительным слоем существенно растут затраты на изготовление платы. Любое увеличение числа слоев сигнальной разводки в платах, работающих на высоких (более 1 ГГц) частотах, удваивает общее число слоев из-за необходимости использования экранных слоев (слоев заземления или питания) между слоями сигнальной разводки.

Чтобы увеличить трассировочное пространство и мобильность трехмерной разводки проводников, проектировщики и производители идут на значительные усложнения технологий, чтобы выполнять в многослойных структурах глухие и скрытые отверстия.

Традиционные технологии изготовления многослойных печатных плат методом металлизации сквозных отверстий не пригодны для монтажа микросхем с матричными выводами с шагом менее 1,0 мм. Но уже созданы корпуса микросхем типа СSP с шагом матричных выводов 0,508 мм (0,020 дюйма) и 0,254 мм (0,010 дюйма). Для монтажа таких компонентов к МПП добавляются специальные слои с глухими ме-

таллизированными отверстиями, на которых реализуется разводка цепей из-под микрокорпусов или из-под бескорпусных кристаллов микросхем. Эти тонкие дополнительные специализированные слои напрессовываются на МПП, после чего в них выполняются глухие металлизированные отверстия. За рубежом данный метод получил название built-up ("надстройка"). И хотя в России еще нет соответствующего устоявшегося понятия, ясно, что термин built-up подразумевает сочетание методов металлизации сквозных отверстий и послойного наращивания, т.е. на русский язык этот термин можно перевести, как "МПП с послойным наращиванием внешних слоев" или "МПП с глухими отверстиями" [3].

Все перечисленные способы несут за собой повышение плотности межсоединений, что является основным вопросом к сохранению технологичности при подготовке производства печатных плат.

Экспериментальные исследования. Предлагаемое техническое решение [4] заключается в снижении плотности межсоединений многослойной печатной платы без увеличения габаритного размера изделия для дополнительного увеличения степени интеграции топологии проводящего рисунка.

Его суть состоит в смещении переходных отверстий непосредственно под контактные площадки выводов микросхем. При изготовлении данной МПП используется технология послойного наращивания с последующим заращиванием глухих переходных отверстий медью.

Задача перетрассировки печатной платы в области BGA накладывает на разработчика дополнительные требования и увеличивает трудоемкость выполняемой работы, т.к. автоматическое выполнение такой операции не предусмотрено в современных САПР печатных плат (САDсистемах).

Данную операцию оптимально выполнять на этапе размещения схемы на печатную плату. Однако с готовыми проектами такая процедура будет означать перетрассировку пространства с нуля.

Поэтому логично было бы перенести выполнение данной операции на математический аппарат САПР этапа конструкторскотехнологической подготовки производства печатной платы (САМ-систему) непосредственно на участке изготовления продукции без привлечения усилий разработчика.

Разработка алгоритма переноса переходных отверстий под контактные площадки BGA и интеграция его в общую CAM-систему – одна из главных задач, которая позволит существенно

снизить трудоемкость перетрассировки серийно выпускаемых печатных плат и перейти к выполнению технологического процесса по изготовлению принципиально новых прототипов изделий электроники.

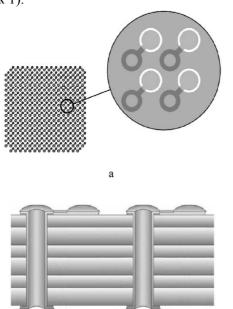

Многослойная печатная плата содержит слои диэлектрического материала, на одной или двух сторонах которого расположен слой проводящего материала, контактные площадки выводов элементов для осуществления электрических соединений между элементами печатной схемы, расположенные в заданных координатах на поверхности МПП, изолирующие прокладки для разделения соседних слоев с рисунками печатных схем, сквозные переходные отверстия для создания межслойных электрических соединений в контактных площадках всех слоев, а также глухие переходные отверстия в наращиваемых на основу слоях. Глухие переходные отверстия предназначены для соединения наружного слоя с одним или несколькими внутренними слоями МПП. Устанавливать переходные отверстия можно разными способами, но наиболее эффективным и часто используемым является установка переходных отверстий по диагонали от контактных площадок для выводов элементов (рисунок 1).

Рисунок 1 — Участок многослойной печатной платы для размещения микросхемы BGA с переходными отверстиями

(а — вид сверху, б — в разрезе)

б

Причем для больших BGA микросхем (>600 выводов) рекомендуется выводить переходные отверстия с каждой стороны платы в разные стороны для уменьшения дефектов при монтаже [5, 6].

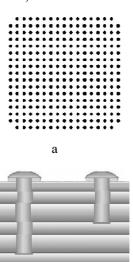

В предлагаемой многослойной печатной плате глухие переходные отверстия в слоях размещены непосредственно под контактными площадками выводов элементов и заращены медью (рисунок 2).

б

Рисунок 2 — Участок многослойной печатной платы для размещения микросхемы BGA с глухими отверстиями под контактными площадками (а — вид сверху, б — в разрезе)

Изготовление многослойной печатной платы осуществляют следующим образом. Формируют основу многослойной печатной платы (например, известным способом фотолитографии), включающую слой диэлектрического материала, слой меди (медной фольги) с одной или двух сторон диэлектрического материала. Осуществляют выполнение рисунка проводников и контактных площадок на фольгированной подлож-Затем поочередно изготавливают последующие слои МПП, каждый из которых содержит слой диэлектрического материала и слой меди. После чего осуществляют сборку МПП методом послойного наращивания (напрессовки) на основу последующих слоев. Метод послойного наращивания заключается в последовательном чередовании слоев, каждый из которых включает диэлектрический материал и проводящий материал. В каждом последующем слое выполняют глухие переходные отверстия на глубину в областях контактных площадок под контакты микросхем. Глухие переходные отверстия в каждом слое заращивают медью. Осуществляют механическую зачистку поверхности каждого слоя для удаления лишней меди, особенно в областях межслойных переходов, где не должно быть наплывов меди. Формируют токопроводящий рисунок проводников и контактных площадок для каждого слоя. После прессования всех слоев заготовки МПП выполняют сверление сквозных переходных отверстий, гальваническое осаждение меди и изготовление топологии внешних слоев.

Использование метода послойного наращивания позволяет получить высокую плотность размещения проводников во всех слоях печатной платы и очень высокую плотность монтажа, вследствие возможности выполнения межслойных переходов в любой точке МПП, независимо от трассировки и расположения межслойных соединений любых смежных слоев.

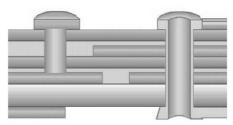

В качестве примера рассмотрим способ изготовления четырехслойной печатной платы для установки микросхемы BGA, с глухими межслойными переходами с первого на третий слой и сквозными переходными отверстиями с первого на последний слой. Формирование данной печатной платы осуществляют методом фотолитографии на фольгированных подложках. На начальном этапе изготавливают основу многослойной печатной платы, состоящую из слоев, не содержащих глухих переходных отверстий. Затем изготавливают второй слой МПП, включающий диэлектрический материал и проводник. Осуществляют сборку в пакет путем напрессовки второго слоя через прокладку на основу МПП методом послойного наращивания. Во втором слое выполняют глухие переходные отверстия на глубину, под контактными площадками для распайки микросхем BGA. Производят заращивание глухих переходных отверстий медью (рисунок 3). Осуществляют механическую подготовку поверхности, нанесение рисунка топологии второго слоя. Аналогично второму слою изготавливают первый слой и через прокладку напрессовывают его на заготовку, содержащую второй, третий и четвертый слои. Выполняют во втором слое глухие переходные отверстия на глубину в области размещения контактных площадок, заращивают их медью. Осуществляют подготовку участков в областях контактных площадок микросхем на установке лазерной подготовки поверхности. Осуществляют сверление сквозных переходных отверстий в собранной МПП и нанесение рисунка внешних слоев (первого и четвертого).

Статистические результаты. Для статистического подтверждения полученных результатов возьмем несколько видов микросхем с массивом шариковых выводов со следующими параметрами:

- шаг 1.5 мм размер КП 0.6 мм;

- шаг 1.27 мм размер КП 0.6 мм;

- шаг 1.0 мм размер КП 0.5 мм;

• шаг 0.75 мм – размер КП 0.3 мм.

В таблице 1 приведены параметры для традиционного способа размещения микросхемы с массивом шариковых выводов.

Из практики производства одним из наиболее технологичных размеров сверла для переходного отверстия является сверло диаметром 0.25 мм. Для опыта оставим этот параметр неизменным.

Рисунок 3 — Разрез четырехслойной печатной платы с глухими межслойными переходными отверстиями с первого на третий слой и сквозными отверстиями с первого на четвертый слой

Таблица 1 – Технологические параметры печатной платы, изготавливаемой по известной технологии

| Шаг микросхемы                                                                 | 1.5   | 1.27  | 1.0   | 0.75  |

|--------------------------------------------------------------------------------|-------|-------|-------|-------|

| КП микросхемы                                                                  | 0.6   | 0.6   | 0.5   | 0.3   |

| Диаметр сверла<br>сквозного переход-<br>ного отверстия                         | 0.25  | 0.25  | 0.25  | 0.25  |

| КП переходного<br>отверстия                                                    | 0.6   | 0.6   | 0.5   | 0.4   |

| Толщина провод-<br>ника                                                        | 0.15  | 0.15  | 0.12  | 0.11  |

| Гарантийный поя-<br>сок                                                        | 0.175 | 0.175 | 0.125 | 0.075 |

| Минимальный за-<br>зор топологии                                               | 0.18  | 0.15  | 0.15  | 0.1   |

| Процент свободно-<br>го трассировочного<br>пространства под<br>микросхемой BGA | 62    | 53    | 52    | 58    |

В таблице 2 приведены параметры для предлагаемого способа.

Таблица 2 — Технологические параметры печатной платы, изготавливаемой предложенным способом

| Шаг микросхемы                                         | 1.5  | 1.27 | 1.0 | 0.75 |

|--------------------------------------------------------|------|------|-----|------|

| КП микросхемы                                          | 0.6  | 0.6  | 0.5 | 0.3  |

| Диаметр сверла<br>сквозного переход-<br>ного отверстия | 0.25 | 0.25 | 0.2 | 0.15 |

| Толщина провод-<br>ника                                                        | 0.15  | 0.15  | 0.12 | 0.11  |

|--------------------------------------------------------------------------------|-------|-------|------|-------|

| Гарантийный поя-<br>сок                                                        | 0.175 | 0.175 | 0.15 | 0.125 |

| Минимальный за-<br>зор топологии                                               | 0.375 | 0.26  | 0.19 | 0.17  |

| Процент свободно-<br>го трассировочного<br>пространства под<br>микросхемой BGA | 72    | 70    | 71   | 78    |

## Продолжение таблицы 2

При условно фиксированной толщине проводников показательными становятся следующие параметры:

- гарантийный поясок толщина медной перемычки от сверла до края КП текстолита (равен половине разности диаметра КП и диаметра сверла);

- минимальный зазор топологии минимальный зазор между парами элементов проводник-проводник, проводник-КП; КП-КП (определяется исходя из разводки печатной платы и регламентируется классами точности [1]);

- процент свободного трассировочного пространства под микросхемой BGA процент не занятой медью поверхности печатной платы (рассчитывается в САПР подготовки производства печатных плат).

Анализируя полученные результаты, отмечаем, что для микросхем с шагами 1.0 мм и 0.75 мм существенно увеличились размеры гарантийных поясков (с 0.125 мм до 0.15 мм и с 0.075 мм до 0.125 мм соответственно).

Минимальный зазор топологии увеличился в среднем в полтора раза, а свободное трассировочное пространство — от 10 до 20 процентов. Полученные результаты позволяют провести как минимум еще один дополнительный проводник аналогичной толщины без сокращения минимального зазора или увеличить толщину проводника для понижения класса точности изготавливаемой платы, что соответственно приведет к снижению трудоемкости и стоимости выпускаемой продукции.

**Выводы.** Результатом использования данного технического решения является заполнение

освобожденных от переходных отверстий мест между контактными площадками выводов микросхемы BGA элементами токопроводящего рисунка. Заращенное переходное отверстие будет выполнять роль контактирующего элемента с выводом микросхемы BGA и одновременно обеспечивать межслойную связь с другими элементами схемы. Кроме того, разработка и внедрение алгоритма, автоматизирующего данную операцию на этапе конструкторско-технологического проектирования, позволят минимизировать время переработки существующих проектов.

Таким образом, снижение плотности межсоединений многослойной печатной платы за счет смещения переходных отверстий под контактные площадки микросхемы BGA и заращивания их медью дает возможность разместить электрическую схему на печатной плате с меньшими габаритными размерами, использовать микросхемы BGA с меньшим шагом, снизить слойность печатной платы, повысить надежность межсоединений, избежать замыканий при установке планарных микросхем и микросхем BGA с использованием поверхностного монтажа, полностью устранить короткие замыкания между токоведущими элементами МПП в процессе пайки.

## Библиографический список

- 1. ГОСТ Р 53429-2009 Платы печатные. Основные параметры конструкции.

- 2. ГОСТ Р 53432-2009 Платы печатные. Основные технические требования к производству.

- 3. *Медведев А., Можаров В.* Плотность межсоединений электрических компонентов // Печатный монтаж. 2011. №3(00032). С. 140-145.

- 4. *Мылов Г.В., Дрожжин И.В.* Патент на полезную модель №144226 «Многослойная печатная плата». Роспатент, 2014.

- 5. *Медведев А.М., Мылов Г.В.* Технологии в производстве электроники. Часть III. Гибкие печатные платы. М.: Группа ИДТ, 2008. 488 с.

- 6. Мылов Г.В., Таганов А.И. Методологические основы автоматизации конструкторско-технологического проектирования гибких многослойных печатных плат. М.: Горячая линия Телеком, 2014. 168 с.